Nano-RAM

| Computer memory and data storage types |

|---|

| Volatile |

| Non-volatile |

Nano-RAM is a proprietary computer memory technology from the company Nantero. It is a type of nonvolatile random-access memory based on the position of carbon nanotubes deposited on a chip-like substrate. In theory, the small size of the nanotubes allows for very high density memories. Nantero also refers to it as NRAM.

Technology

[edit]The first generation Nantero NRAM technology was based on a three-terminal semiconductor device where a third terminal is used to switch the memory cell between memory states. The second generation NRAM technology is based on a two-terminal memory cell. The two-terminal cell has advantages such as a smaller cell size, better scalability to sub-20 nm nodes (see semiconductor device fabrication), and the ability to passivate the memory cell during fabrication.

In a non-woven fabric matrix of carbon nanotubes (CNTs), crossed nanotubes can either be touching or slightly separated depending on their position. When touching, the carbon nanotubes are held together by Van der Waals forces.[1] Each NRAM "cell" consists of an interlinked network of CNTs located between two electrodes as illustrated in Figure 1. The CNT fabric is located between two metal electrodes, which is defined and etched by photolithography, and forms the NRAM cell.

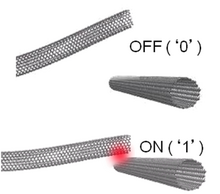

The NRAM acts as a resistive non-volatile random-access memory (RAM) and can be placed in two or more resistive modes depending on the resistive state of the CNT fabric. When the CNTs are not in contact the resistance state of the fabric is high and represents an "off" or "0" state. When the CNTs are brought into contact, the resistance state of the fabric is low and represents an "on" or "1" state. NRAM acts as a memory because the two resistive states are very stable. In the 0 state, the CNTs (or a portion of them) are not in contact and remain in a separated state due to the stiffness of the CNTs resulting in a high resistance or low current measurement state between the top and bottom electrodes. In the 1 state, the CNTs (or a portion of them) are in contact and remain contacted due to Van der Waals forces between the CNTs, resulting in a low resistance or high current measurement state between the top and bottom electrodes. Note that other sources of resistance such as contact resistance between electrode and CNT can be significant and also need to be considered.

To switch the NRAM between states, a small voltage greater than the read voltage is applied between top and bottom electrodes. If the NRAM is in the 0 state, the voltage applied will cause an electrostatic attraction between the CNTs close to each other causing a SET operation. After the applied voltage is removed, the CNTs remain in a 1 or low resistance state due to physical adhesion (Van der Waals force) with an activation energy (Ea) of approximately 5eV. If the NRAM cell is in the 1 state, applying a voltage greater than the read voltage will generate CNT phonon excitations with sufficient energy to separate the CNT junctions. This is the phonon driven RESET operation. The CNTs remain in the OFF or high resistance state due to the high mechanical stiffness (Young's Modulus 1 TPa) with an activation energy (Ea) much greater than 5 eV. Figure 2 illustrates both states of an individual pair of CNTs involved in the switch operation. Due to the high activation energy (> 5eV) required for switching between states, the NRAM switch resists outside interference like radiation and operating temperature that can erase or flip conventional memories like DRAM.

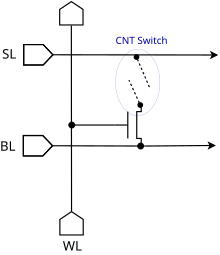

NRAMs are fabricated by depositing a uniform layer of CNTs onto a prefabricated array of drivers such as transistors as shown in Figure 1. The bottom electrode of the NRAM cell is in contact with the underlying via (electronics) connecting the cell to the driver. The bottom electrode may be fabricated as part of the underlying via or it may be fabricated simultaneously with the NRAM cell, when the cell is photolithographically defined and etched. Before the cell is photolithographically defined and etched, the top electrode is deposited as a metal film onto the CNT layer so that the top metal electrode is patterned and etched during the definition of the NRAM cell. Following the dielectric passivation and fill of the array, the top metal electrode is exposed by etching back the overlying dielectric using a smoothing process such as chemical-mechanical planarization. With the top electrode exposed, the next level of metal wiring interconnect is fabricated to complete the NRAM array. Figure 3 illustrates one circuit method to select a single cell for writing and reading. Using a cross-grid interconnect arrangement, the NRAM and driver, (the cell), forms a memory array similar to other memory arrays. A single cell can be selected by applying the proper voltages to the word line (WL), bit line (BL), and select lines (SL) without disturbing the other cells in the array. Alternatively between the bottom electrode and top metal layer they may be two layers of CNTs: one with uniformly arranged CNTs, and another with randomly arranged CNTs. The uniformly arranged CNTs are used to protect the randomly arranged CNTs from the top metal layer.[2]

Characteristics

[edit]NRAM has a density, at least in theory, similar to that of DRAM. DRAM includes capacitors, which are essentially two small metal plates with a thin insulator between them. NRAM has terminals and electrodes roughly the same size as the plates in a DRAM, the nanotubes between them being so much smaller they add nothing to the overall size. However it seems there is a minimum size at which a DRAM can be built, below which there is simply not enough charge being stored on the plates. NRAM appears to be limited only by lithography[citation needed]. This means that NRAM may be able to become much denser than DRAM, perhaps also less expensive. Unlike DRAM, NRAM does not require power to "refresh" it, and will retain its memory even after power is removed. Thus the power needed to write and retain the memory state of the device is much lower than DRAM, which has to build up charge on the cell plates. This means that NRAM might compete with DRAM in terms of cost, but also require less power, and as a result also be much faster because write performance is largely determined by the total charge needed. NRAM can theoretically reach performance similar to SRAM, which is faster than DRAM but much less dense, and thus much more expensive.

Comparison with other non-volatile memory

[edit]Compared with other non-volatile random-access memory (NVRAM) technologies, NRAM has several advantages. In flash memory, the common form of NVRAM, each cell resembles a MOSFET transistor with a control gate (CG) modulated by a floating gate (FG) interposed between the CG and the FG. The FG is surrounded by an insulating dielectric, typically an oxide. Since the FG is electrically isolated by the surrounding dielectric, any electrons placed on the FG will be trapped on the FG which screens the CG from the channel of the transistor and modifies the threshold voltage (VT) of the transistor. By writing and controlling the amount of charge placed on the FG, the FG controls the conduction state of the MOSFET flash device depending on the VT of the cell selected. The current flowing through the MOSFET channel is sensed to determine the state of the cell forming a binary code where a 1 state (current flow) when an appropriate CG voltage is applied and a 0 state (no current flow) when the CG voltage is applied.

After being written to, the insulator traps electrons on the FG, locking it into the 0 state. However, in order to change that bit, the insulator has to be "overcharged" to erase any charge already stored in it. This requires higher voltage, about 10 volts, much more than a battery can provide. Flash systems include a "charge pump" that slowly builds up power and releases it at higher voltage. This process is not only slow, but degrades the insulators. For this reason flash has a limited number of writes before the device will no longer operate effectively.

NRAM reads and writes are both "low energy" in comparison to flash (or DRAM for that matter due to "refresh"), meaning NRAM could have longer battery life. It may also be much faster to write than either, meaning it may be used to replace both. Modern phones include flash memory for storing phone numbers, DRAM for higher performance working memory because flash is too slow, and some SRAM for even higher performance. Some NRAM could be placed on the CPU to act as the CPU cache, and more in other chips replacing both the DRAM and flash.

NRAM is one of a variety of new memory systems, many of which claim to be "universal" in the same fashion as NRAM – replacing everything from flash to DRAM to SRAM.

An alternative memory ready for use is ferroelectric RAM (FRAM or FeRAM). FeRAM adds a small amount of a ferro-electric material to a DRAM cell. The state of the field in the material encodes the bit in a non-destructive format. FeRAM has advantages of NRAM, although the smallest possible cell size is much larger than for NRAM. FeRAM is used in applications where the limited number of writes of flash is an issue. FeRAM read operations are destructive, requiring a restoring write operation afterwards.

Other more speculative memory systems include magnetoresistive random-access memory (MRAM) and phase-change memory (PRAM). MRAM is based on a grid of magnetic tunnel junctions. MRAM's reads the memory using the tunnel magnetoresistance effect, allowing it to read the memory both non-destructively and with very little power. Early MRAM used field induced writing,[3] reached a limit in terms of size, which kept it much larger than flash devices. However, new MRAM techniques might overcome the size limitation to make MRAM competitive even with flash memory. The techniques are Thermal Assisted Switching (TAS),[4] developed by Crocus Technology, and Spin-transfer torque on which Crocus, Hynix, IBM, and other companies were working in 2009.[5]

PRAM is based on a technology similar to that in a writable CD or DVD, using a phase-change material that changes its magnetic or electrical properties instead of its optical ones. The PRAM material itself is scalable but requires a larger current source.

History

[edit] | |

| Company type | Private |

|---|---|

| Industry | Semiconductors, nanotechnology |

| Founded | 2001 |

| Headquarters | , US |

| Products | Nano-RAM |

| Website | www |

Nantero was founded in 2001, and headquartered in Woburn, Massachusetts. Due to the massive investment in flash semiconductor fabrication plants, no alternative memory has replaced flash in the marketplace, despite predictions as early as 2003 of the impending speed and density of NRAM.[6][7]

In 2005, NRAM was promoted as universal memory, and Nantero predicted it would be in production by the end of 2006.[8] In August 2008, Lockheed Martin acquired an exclusive license for government applications of Nantero's intellectual property.[9]

By early 2009, Nantero had 30 US patents and 47 employees, but was still in the engineering phase.[10] In May 2009, a radiation-resistant version of NRAM was tested on the STS-125 mission of the US Space Shuttle Atlantis.[11]

The company was quiet until another round of funding and collaboration with the Belgian research center imec was announced in November 2012.[12][13] Nantero raised a total of over $42 million through the November 2012 series D round.[14] Investors included Charles River Ventures, Draper Fisher Jurvetson, Globespan Capital Partners, Stata Venture Partners and Harris & Harris Group. In May 2013, Nantero completed series D with an investment by Schlumberger.[15] EE Times listed Nantero as one of "10 top startups to watch in 2013".[16]

31 Aug 2016: Two Fujitsu semiconductor businesses are licensing Nantero NRAM technology with joint Nantero–Fujitsu development to produce chips, announced in 2018. They are announced to have several thousand times faster rewrites and many thousands of times more rewrite cycles than embedded flash memory.[17] As of 2024, these products are still announced but have not reached the market.

See also

[edit]References

[edit]- ^ "What is DRAM's Future?". 9 April 2020.

- ^ "What is DRAM's Future?". 9 April 2020.

- ^ Slaughter, J. M.; Rizzo, N. D.; Mancoff, F. B.; Whig, R.; Smith, K.; Aggarwal, S.; Tehrani, S. (2010). "Toggle and Spin- Toggle and Spin-Torque MRAM: Status and OutlooK" (PDF). Magnetic Society of Japan. 5. Everspin Technologies: 171. S2CID 112533665. Retrieved 2 December 2022.

- ^ The Emergence of Practical MRAM "Archived copy" (PDF). Archived from the original (PDF) on 2011-04-27. Retrieved 2009-07-20.

{{cite web}}: CS1 maint: archived copy as title (link) - ^ Mark LaPedus (June 18, 2009). "Tower invests in Crocus, tips MRAM foundry deal". EE Times. Retrieved July 10, 2013.

- ^ "A new type of computer memory uses carbon, rather than silicon". The Economist. May 8, 2003. Retrieved July 10, 2013.

- ^ John Leyden (May 13, 2003). "On ultra-fast carbon memory: Nanotube". The Register. Retrieved July 20, 2013.

- ^ "Nanotube 'Universal Memory' A Turn-On For Computers". Museum of Science Current Science and Technology Center. Archived from the original on February 4, 2005. Retrieved July 14, 2013.

- ^ LaPedus, Mark (August 13, 2008). "Lockheed buys Nantero's government unit". Retrieved August 20, 2013.

- ^ Efrain Viscarolasaga (January 22, 2009). "Nantero's semiconductors pull high patent power ranking". Mass High Tech. Retrieved July 10, 2013.

- ^ "Lockheed Martin Tests Carbon Nanotube-Based Memory Devices on NASA Shuttle Mission". Press release. November 18, 2009. Retrieved July 14, 2013.

- ^ "Nantero, imec Collaborate on Development of Carbon-Nanotube-Based Memory". AZOM: The A to Z of Materials. November 1, 2012. Retrieved August 20, 2013.

- ^ Mellow, Chris (November 6, 2012). "Flash-killer nanotube memory firm teams with Belgians to try again: 3 yrs late, and counting - but now moving 'even faster'". The Register. Retrieved July 10, 2013.

- ^ Resende, Patricia (November 28, 2012). "Nantero gets $10M to move product into commercialization". Mass High Tech. Retrieved July 10, 2013.

- ^ "Nantero Secures Second Closing of Series D; Company Adds Major Strategic Investors". May 29, 2013. Archived from the original on June 30, 2013. Retrieved August 20, 2013.

- ^ Clarke, Peter (December 21, 2012). "10 top startups to watch in 2013". EE Times. Retrieved July 10, 2013.

- ^ Mellor, Chris (31 August 2016). "Deep inside Nantero's non-volatile carbon nanotube RAM tech". The Register.